- 全部

- 默认排序

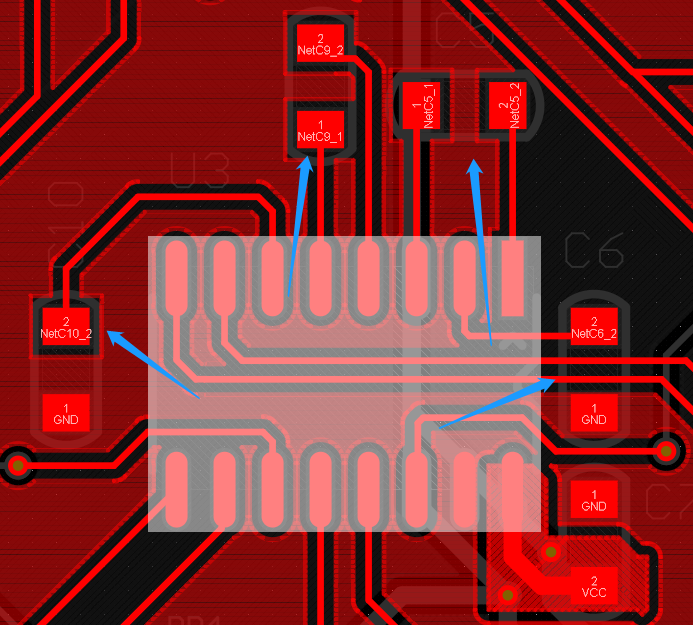

注意此处的滤波电容位置,是要先大后小放置:先是放置C289然后再是C13-16此处网络是否没有连接上:此处电容位置一致问题,同样的问题自己检查修改下,不一一截图指出:电容按照电源输出方向,按照先大后小的顺序布局。输出电源主干道的滤波电容都要

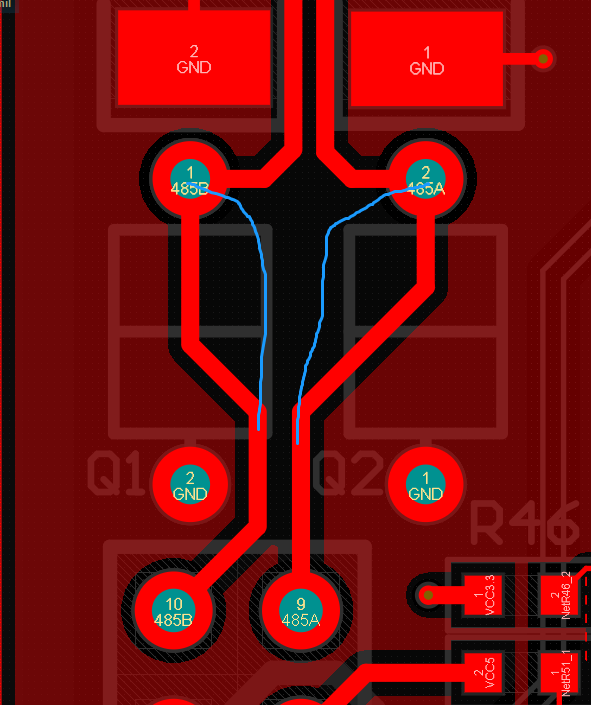

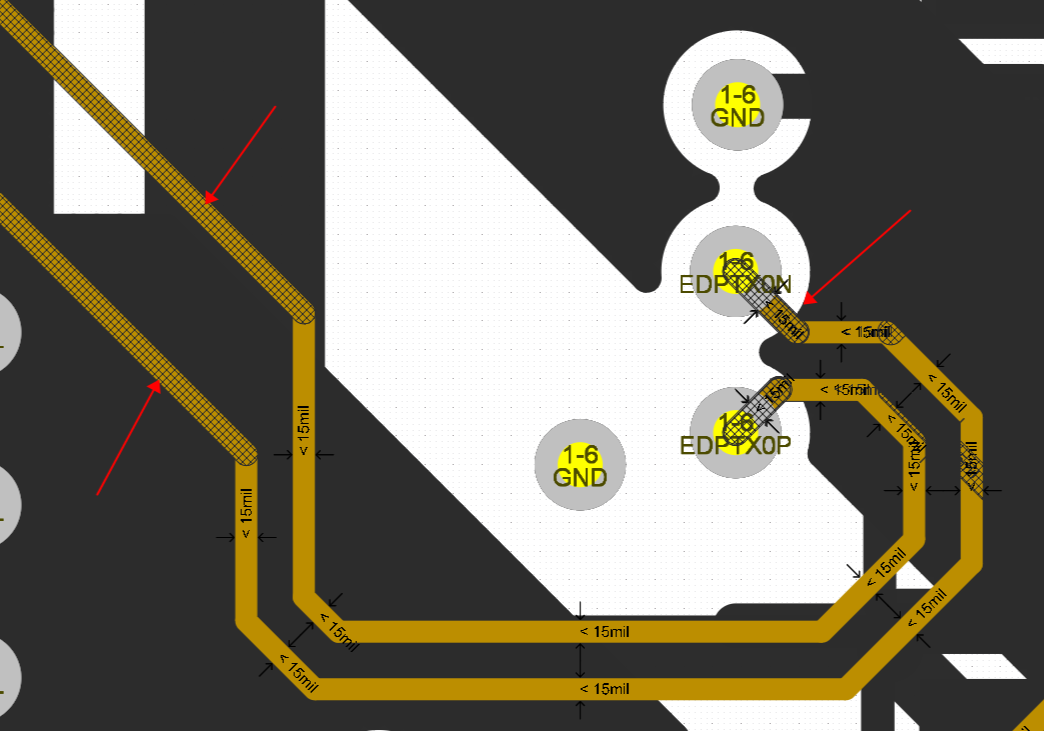

1.485需要走内差分2.网口除差分信号外,其他的都需要加粗到20mil3.差分对内等长5mil4.跨接器件 旁边尽量多打地过孔,分割间距尽量1mm以上5.模拟信号走线需要加粗6.电感所在层的内部需要挖空处理7.电源输入滤波电容法尽量靠近管

1.232的升压电容走线需要加粗2.走线不要从电阻电容中间穿,后期容易造成短路3.USB差分孔90欧姆,需要添加差分对,对内等长误差5mil4.输出滤波电容先大后小摆放5.注意输入输出需要满足载流,尽量铺铜处理6.电源打孔需要打在滤波电容后

在电子设计自动化(EDA)领域内,Altium Designer(简称:AD)和Pads是两款电子工程师常用的PCB设计软件,在使用过程中难免会遇见将AD文件转换成Pads文件格式问题,本文将详细介绍这一过程,希望对你有所帮助。1、准备工作

在电子工程设计中,选择适合自己需求的EDA工具非常重要,Altium Designer(简称:AD)是一款功能强大界面简洁的EDA软件,而立创EDA是立创商城推出的一款在线PCB设计工具,对工程师来说,可能需要将AD文件导入立创EDA中进行

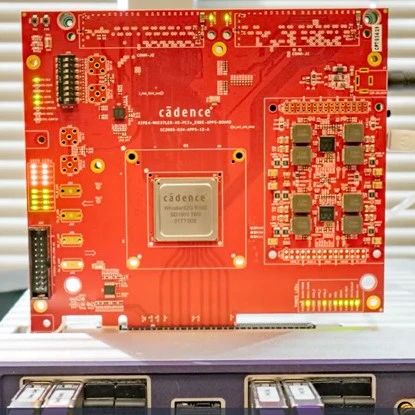

从规范草案到被 PCI-SIG 列入集成商的合规目录需要经历数年。初步 PCIe 5.0 规范于 2017 年 6 月公布,最终规范于 2019 年 5 月发布,第一次正式合规研讨会于 2022 年 4 月举行。如此漫长的过程说明了所开发的产品以及支持这些产品所需的生态系统非常复杂。Cadence

之前更新的AD转换电路系列文谈了闪烁型AD电路、电容积分型AD电路和逐次逼近型AD转换电路,接下来我们来聊聊∑-△型AD电路和流水线型AD电路,希望对小伙伴们有所帮助。想看之前系列文可点击右侧链接《AD转换电路的工作原理及分类(上)》和《A

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.过孔离存在多余的线头3.地网络直接就近打孔连接到地儿层的地平面即可4.确认一下此处是否满足载流5.有stub线6.走线未连接到焊盘中心7.USB的两根信号需要控90Ohm的

声明:本破解教程由凡亿教育-郑老师(Kivy)精心编写作,仅供个人及 Altium Designer 粉丝们交流学习之用,请勿用于商业用途, 谢谢支持 安装包下载:关注右侧公众微信号回复关键词“AD23安装包”获取下载地址 全文教程步骤预览

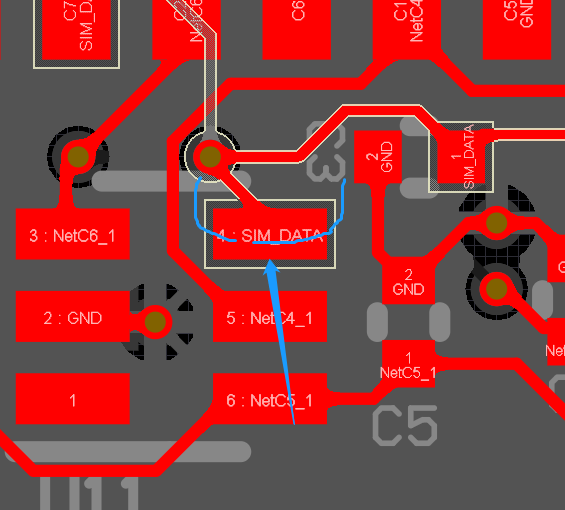

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

扫码关注

扫码关注